# Intel® PXA27x Processor Family

**Design Guide**

May 2005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® PXA27x Processor Family may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact the local Intel sales office or the distributor to obtain the latest specifications and before placing the product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2005

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel Insusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel Quick Capture Technology, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, Quick Capture Technology, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, VTune, and Wireless Intel SpeedStep Technology are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

### Part I

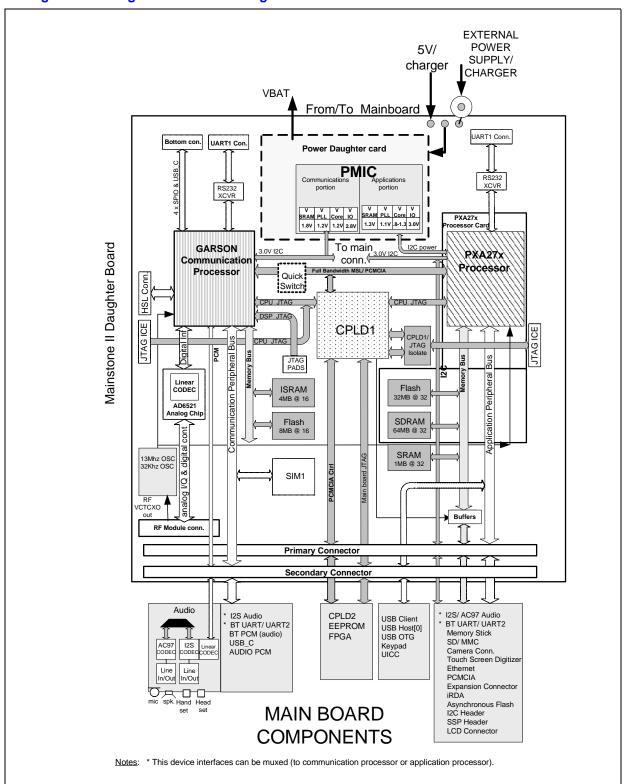

| 1 | Intro                                                       | duction to Part I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l: 1-1                                                            |

|---|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

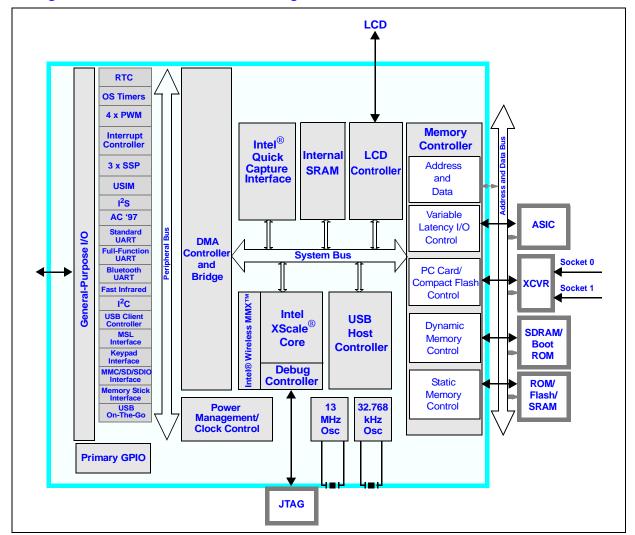

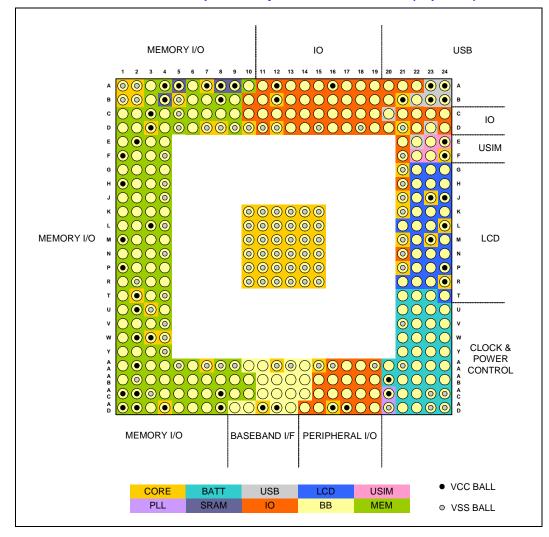

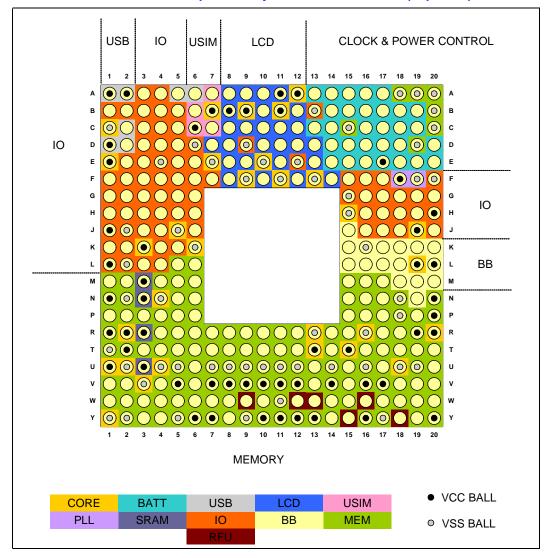

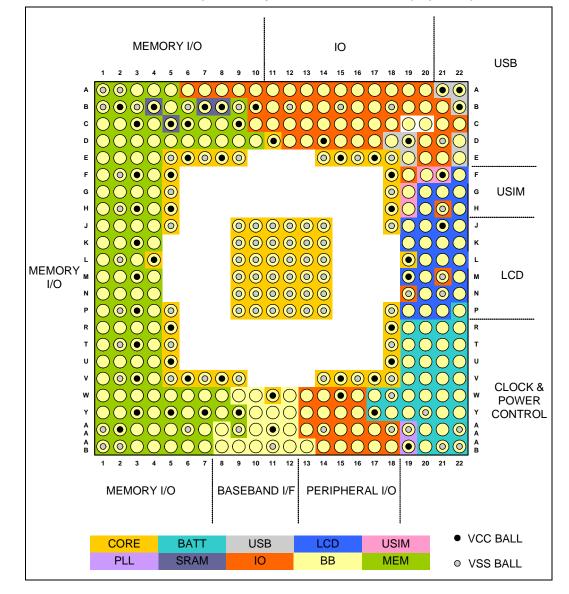

|   | 1.1<br>1.2<br>1.3<br>1.4                                    | Document Organization and Overview Functional Overview Package Introduction Signal Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | l: 1-2<br>l: 1-3                                                  |

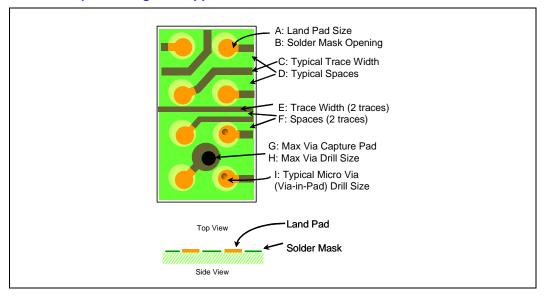

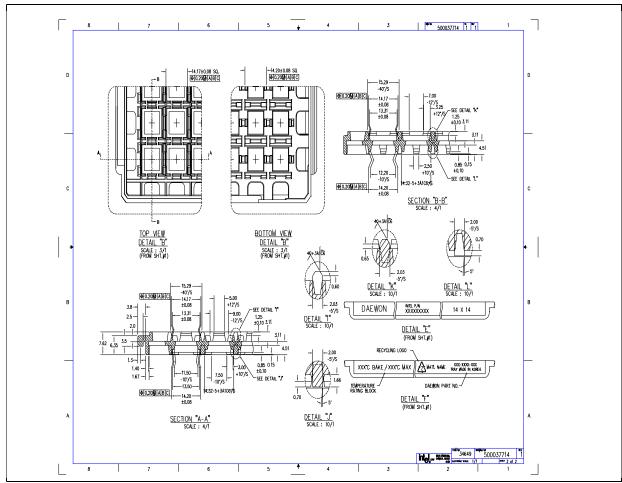

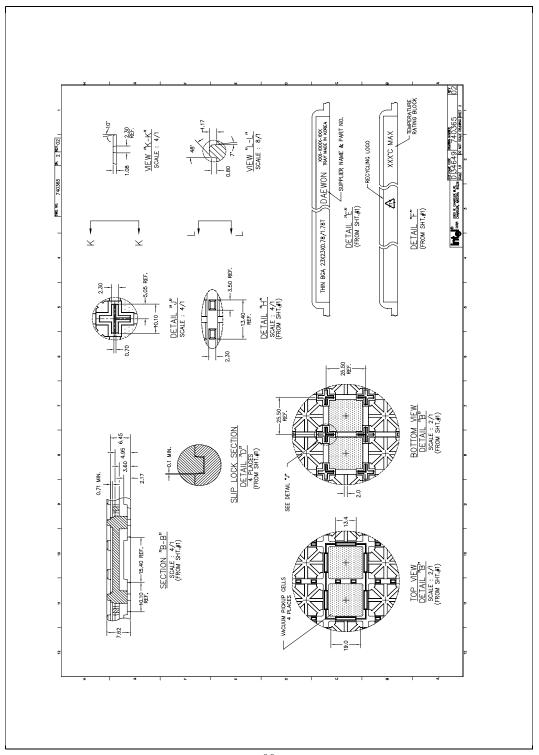

| 2 | PCB                                                         | Design Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I: 2-1                                                            |

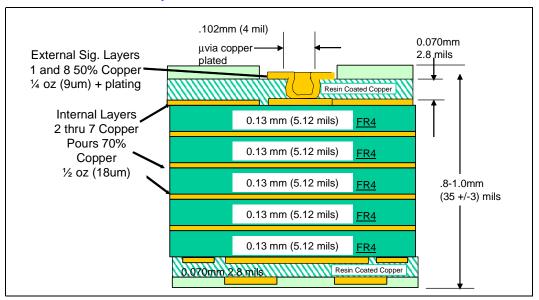

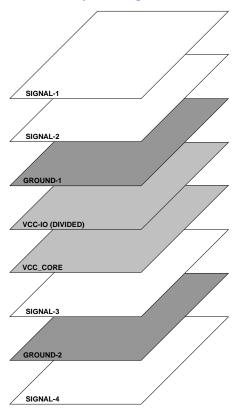

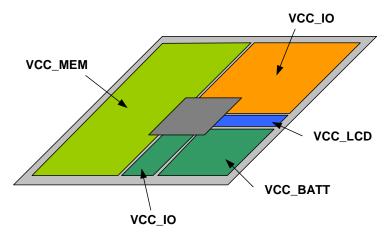

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Intel® Flash Memory Design Guidelines  General PCB Characteristics  2.2.1 PCB Layer Assignment (Stackup)  2.2.2 PCB Component Placement  2.2.3 PCB Escape Routing  2.2.3.1 VF-BGA Escape Routing  2.2.3.2 FS-CSP Escape Routing  2.2.3.3 PBGA Escape Routing  2.2.3.3 PBGA Escape Routing  2.2.4 PCB Keep-out Zones  2.2.5 Recommended Mobile Handset Dimensions  Power Supply Decoupling Requirements  Thermal Considerations  Package to Board Assembly Process  Silicon Daisy Chain (SDC) Evaluation Units  Handling: Shipping Media  Preconditioning and Moisture Sensitivity  Tray Specifications | l: 2-1l: 2-2l: 2-7l: 2-7l: 2-8l: 2-10l: 2-11l: 2-12l: 2-12l: 2-12 |

| 3 | Desi                                                        | gn Check List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I: 3-1                                                            |

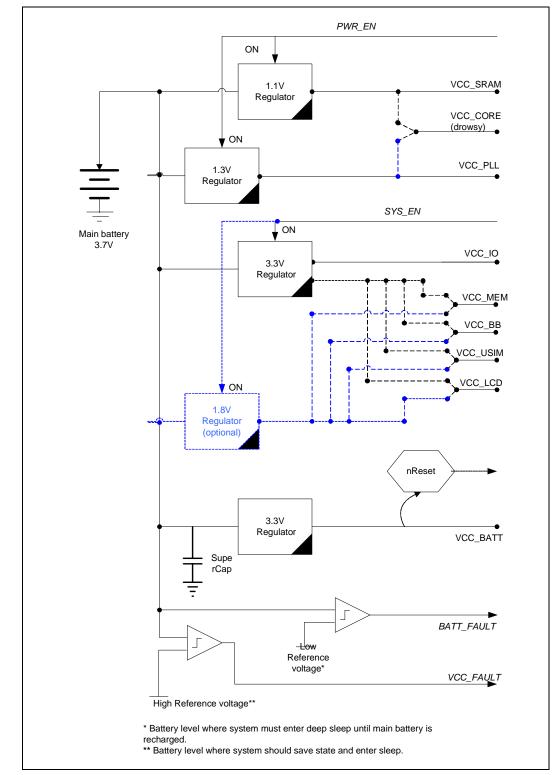

| 4 | Mixe                                                        | d Voltage Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I: 4-1                                                            |

|   | 4.1<br>4.2<br>4.3<br>4.4                                    | Overview  Required Power Supplies  Example Power Supply Utilizing Minimal Regulators  Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l: 4-1<br>l: 4-2                                                  |

| 5 |                                                             | er Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

| • | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | l: 5-1<br>l: 5-1<br>l: 5-1<br>l: 5-2<br>l: 5-2<br>l: 5-3          |

|   | 5.6<br>5.7                                                  | Achieve Minimum Power Usage During StandbyAchieve Minimum Power Usage During Idle/13M/Run/Turbo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

### Part II

| 1 | Intro | duction  | to Part II  |                                                        | II: 1-1 |  |

|---|-------|----------|-------------|--------------------------------------------------------|---------|--|

| 2 | Pack  | age and  | l Pins      |                                                        | II: 2-1 |  |

| 3 | Cloc  | ks and F | Power Inte  | erface                                                 | II: 3-1 |  |

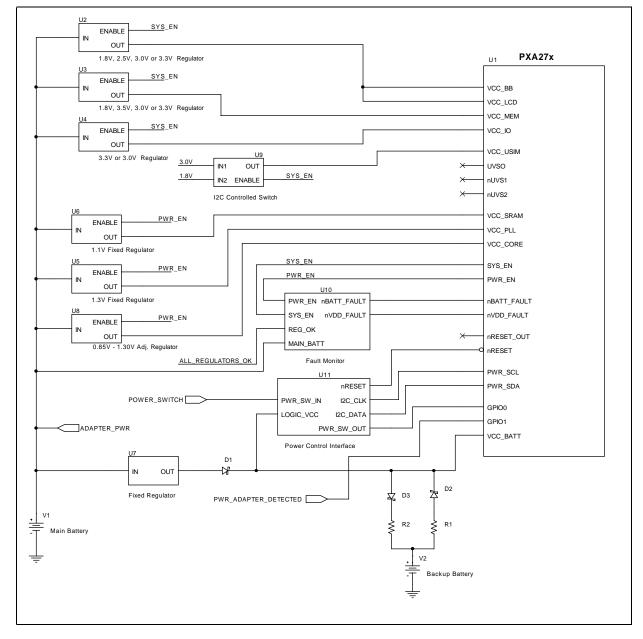

|   | 3.1   | Overview |             |                                                        |         |  |

|   | 3.2   | Signals  |             |                                                        |         |  |

|   |       | 3.2.1    |             | terface Signals                                        |         |  |

|   |       | 3.2.2    |             | Nanager Interface Control Signals                      |         |  |

|   |       | 3.2.3    | Power E     | nable (PWR_EN)                                         | II: 3-3 |  |

|   |       |          | 3.2.3.1     | System Power Enable (SYS_EN)                           | II: 3-3 |  |

|   |       |          | 3.2.3.2     | Power Manager I2C Clock (PWR_SCL)                      | II: 3-3 |  |

|   |       |          | 3.2.3.3     | Power Manager I2C Data (PWR_SDA)                       |         |  |

|   |       |          | 3.2.3.4     | nVDD_FAULT                                             |         |  |

|   |       |          | 3.2.3.5     | nBATT_FAULT                                            |         |  |

|   | 3.3   |          |             |                                                        |         |  |

|   | 3.4   |          |             |                                                        |         |  |

|   | 3.5   |          |             | tions                                                  |         |  |

|   |       | 3.5.1    |             | terface                                                |         |  |

|   |       |          | 3.5.1.1     | Using the On-Chip Oscillator with a 32.768-KHz Crystal |         |  |

|   |       |          | 3.5.1.2     | Using an External 32.768-KHz Clock                     |         |  |

|   |       |          | 3.5.1.3     | Using the On-Chip Oscillator with a 13.000-MHz Crystal |         |  |

|   |       | 0.50     | 3.5.1.4     | Using an External 13.00-MHz Clock                      |         |  |

|   |       | 3.5.2    |             | nterface                                               |         |  |

|   |       |          | 3.5.2.1     | Power Supplies                                         |         |  |

| 4 |       |          |             |                                                        |         |  |

|   | 4.1   |          |             |                                                        |         |  |

|   | 4.2   | -        |             |                                                        |         |  |

|   | 4.3   |          |             |                                                        |         |  |

|   | 4.4   | Layout   | Notes       |                                                        | II: 4-2 |  |

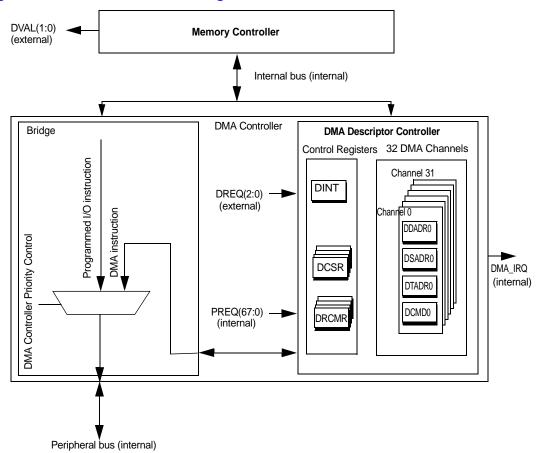

| 5 | DMA   | Contro   | ller Interf | ace                                                    | II: 5-1 |  |

|   | 5.1   | Overvi   | ew          |                                                        | II: 5-1 |  |

|   | 5.2   | Signals  | S           |                                                        | II: 5-1 |  |

|   | 5.3   | Block [  | Diagram     |                                                        | II: 5-2 |  |

|   | 5.4   | Layout   | Notes       |                                                        | II: 5-2 |  |

|   | 5.5   | Modes    | of Opera    | tion                                                   | II: 5-3 |  |

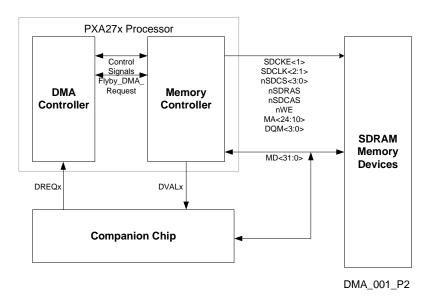

|   |       | 5.5.1    | Fly-By D    | DMA Transfers                                          | II: 5-3 |  |

|   |       |          | 5.5.1.1     | Signals                                                | II: 5-3 |  |

|   |       |          | 5.5.1.2     | Block Diagram                                          | II: 5-4 |  |

|   |       |          | 5.5.1.3     | Layout Notes                                           |         |  |

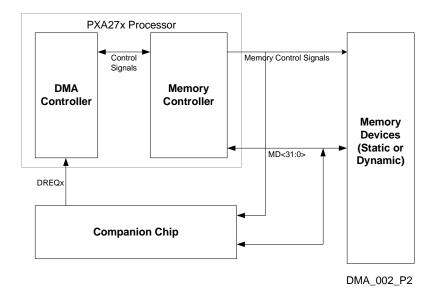

|   |       | 5.5.2    | Flow-Th     | rough DMA Transfers                                    | II: 5-5 |  |

|   |       |          | 5.5.2.1     | Signals                                                |         |  |

|   |       |          | 5.5.2.2     | Block Diagram                                          |         |  |

|   |       |          | 5.5.2.3     | Layout Notes                                           | II: 5-6 |  |

| 6 | Syst  | em Mem   | ory Inter   | face                                                   | II: 6-1 |  |

|   | 6.1   | Overvi   | ew          |                                                        | II: 6-1 |  |

|   | 6.2   | Signals  | S           |                                                        | II: 6-3 |  |

|   | 6.3 | Block F  | agram       |                                                                | II: 6   | -5 |

|---|-----|----------|-------------|----------------------------------------------------------------|---------|----|

|   | 6.4 | Memor    | y Controlle | er Layout Notes                                                | II: 6   | -6 |

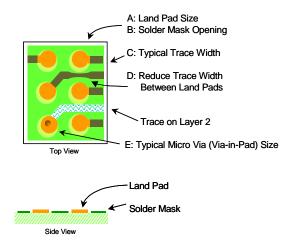

|   |     | 6.4.1    | Memory      | Controller Routing Guidelines for 0.5mm and 0.65 mm Ball Pitch | II: 6   | -6 |

|   |     |          | 6.4.1.1     | System Bus Recommended Signal Routing Guidelines               |         |    |

|   |     |          | (Excludin   | ng SDCLK <x> and SDCAS)</x>                                    | II: 6   | -6 |

|   |     |          | 6.4.1.2     | SDCLK and SDCAS Recommended Signal Routing Guidelines          |         |    |

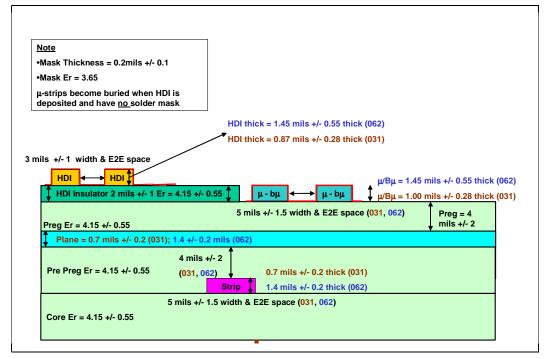

|   |     |          | 6.4.1.3     | Minimum Board Stack-up Configuration used for Signal Integrity | II: 6   | -8 |

|   | 6.5 | Modes    | of Operati  | ion Overview                                                   | II: 6   | -9 |

|   |     | 6.5.1    | SDRAM       | Interface                                                      | II: 6   | -9 |

|   |     |          | 6.5.1.1     | SDRAM Signals                                                  | II: 6   | -9 |

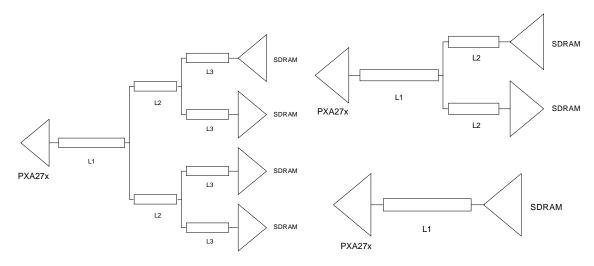

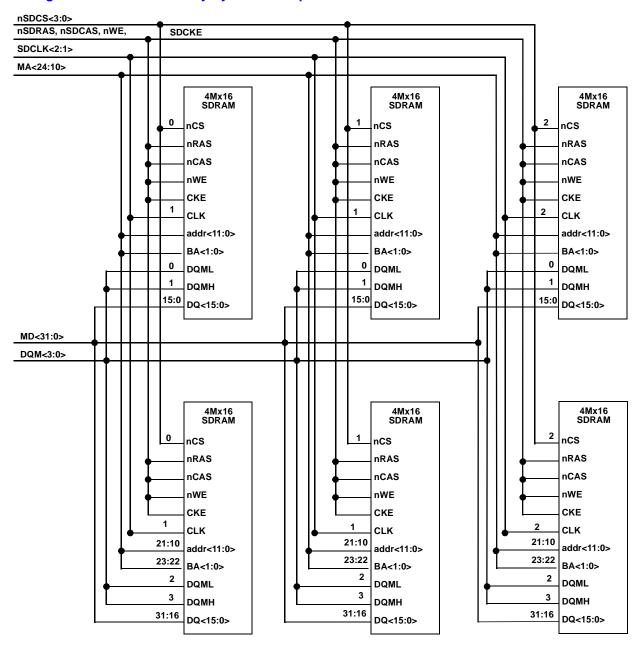

|   |     |          | 6.5.1.2     | SDRAM Memory Block Diagram                                     | II: 6-  | 11 |

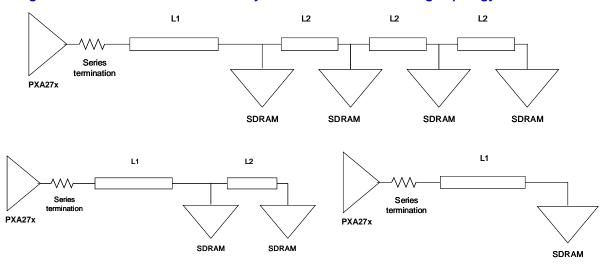

|   |     |          | 6.5.1.3     | SDRAM Layout Notes                                             |         |    |

|   |     | 6.5.2    | Flash Me    | emory Interface (Asynchronous/Synchronous)                     | II: 6-1 | 15 |

|   |     |          | 6.5.2.1     | Flash Memory Signals                                           | II: 6-1 | 15 |

|   |     |          | 6.5.2.2     | Flash Block Diagram                                            |         |    |

|   |     |          | 6.5.2.3     | Flash Layout Note                                              | II: 6-  | 16 |

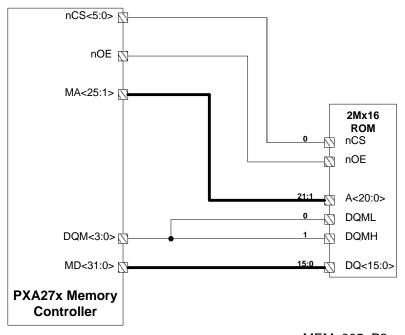

|   |     | 6.5.3    | ROM Inte    | erface                                                         | II: 6-1 | 17 |

|   |     |          | 6.5.3.1     | ROM Signals                                                    | II: 6-1 | 17 |

|   |     |          | 6.5.3.2     | ROM Block Diagram                                              |         |    |

|   |     |          | 6.5.3.3     | ROM Layout Notes                                               |         |    |

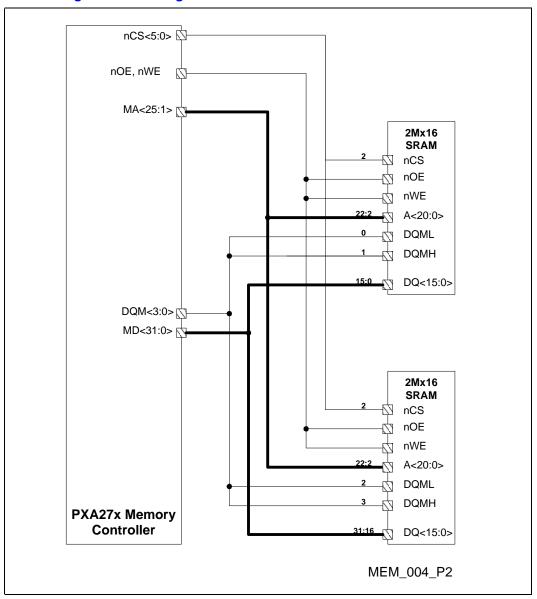

|   |     | 6.5.4    | SRAM In     | terface                                                        | II: 6-1 | 18 |

|   |     |          | 6.5.4.1     | SRAM Signals                                                   |         |    |

|   |     |          | 6.5.4.2     | SRAM Block Diagram                                             | II: 6-2 | 20 |

|   |     |          | 6.5.4.3     | SRAM Layout Notes                                              |         |    |

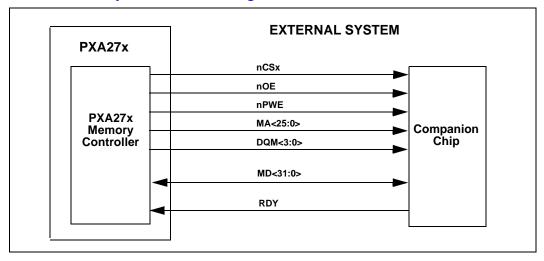

|   |     | 6.5.5    | Variable    | Latency Input/Output (VLIO) Interface                          |         |    |

|   |     |          | 6.5.5.1     | VLIO Memory Signals                                            | II: 6-2 | 22 |

|   |     |          | 6.5.5.2     | VLIO Block Diagram                                             |         |    |

|   |     |          | 6.5.5.3     | VLIO Memory Layout Notes                                       |         |    |

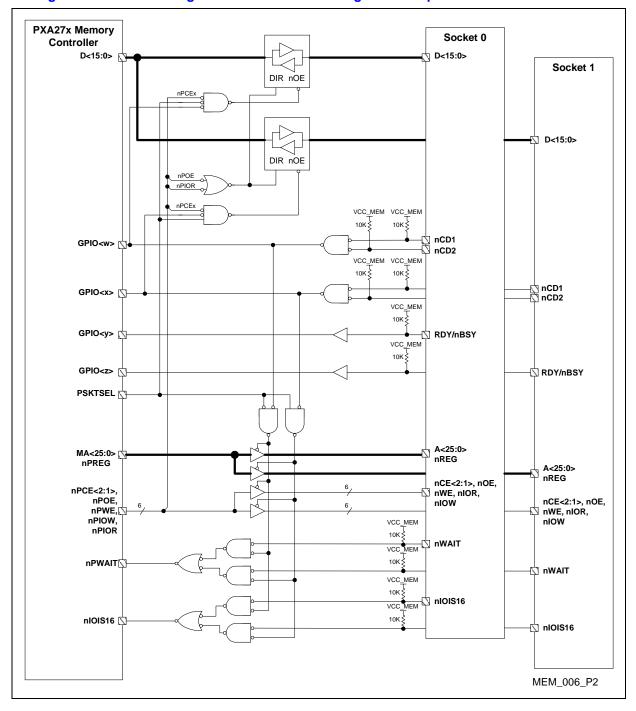

|   |     | 6.5.6    | PC Card     | (PCMCIA) Interface                                             |         |    |

|   |     |          | 6.5.6.1     | PC Card Signals                                                |         |    |

|   |     |          | 6.5.6.2     | PC-Card Block Diagrams                                         |         |    |

|   |     |          | 6.5.6.3     | PC Card Layout Notes                                           |         |    |

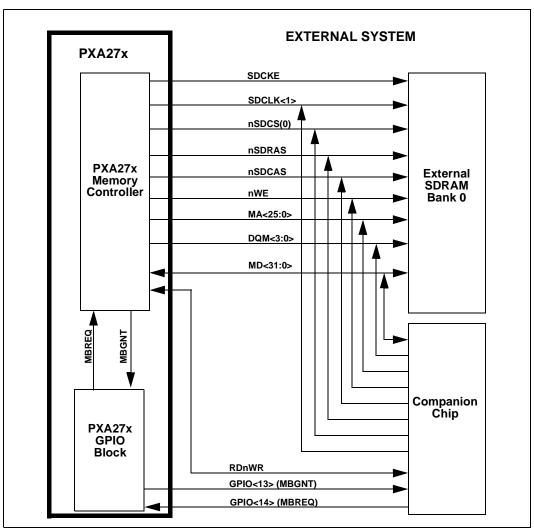

|   |     | 6.5.7    | Alternate   | Bus Master Interface                                           | II: 6-2 | 29 |

|   |     |          | 6.5.7.1     | Alternate Bus Master Signals                                   |         |    |

|   |     |          | 6.5.7.2     | Alternate Bus Master Block Diagram                             |         |    |

|   |     |          | 6.5.7.3     | Alternate Bus Master Layout Notes                              | II: 6-3 | 32 |

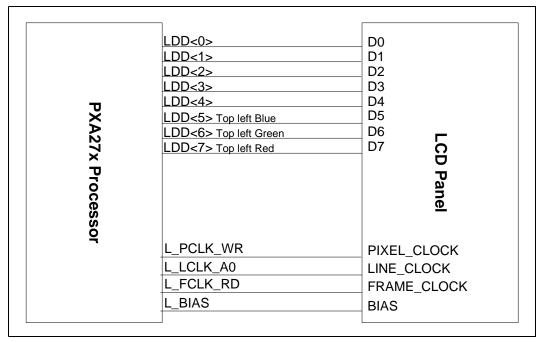

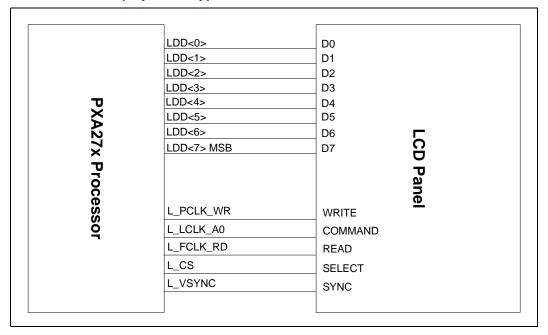

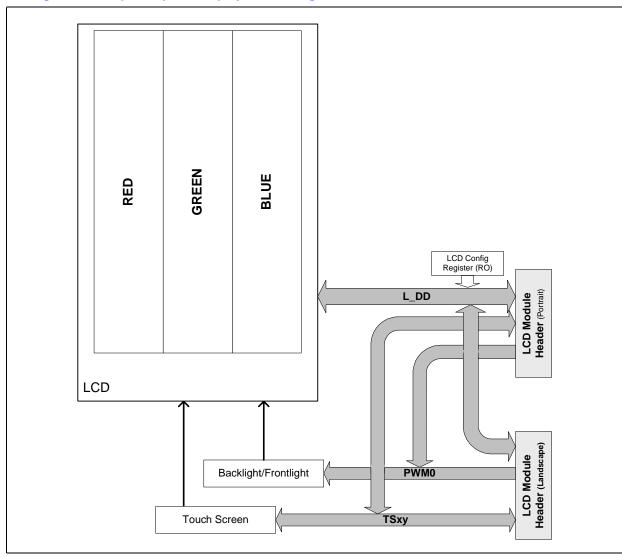

| 7 | LCD | Interfac | e           |                                                                | ll: 7   | -1 |

|   | 7.1 | Overvi   | ew          |                                                                | ll: 7   | -1 |

|   | 7.2 | Signals  | 3           |                                                                | II: 7   | -2 |

|   | 7.3 | Schem    | atics/Blocl | k Diagram                                                      | II: 7   | -3 |

|   | 7.4 |          |             | •                                                              |         |    |

|   |     | 7.4.1    |             | Voltage                                                        |         |    |

|   |     | 7.4.2    |             | t Inverter                                                     |         |    |

|   |     | 7.4.3    |             | outing and Buffering                                           |         |    |

|   |     | 7.4.4    |             | onnector                                                       |         |    |

|   | 7.5 |          |             | ion Overview                                                   |         |    |

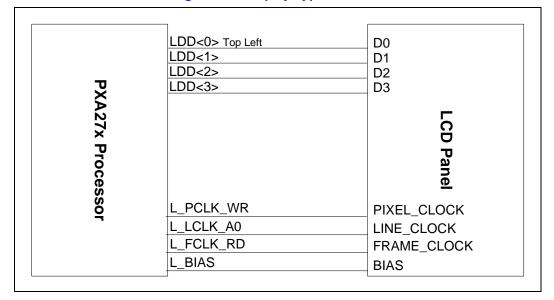

|   | 0   | 7.5.1    |             | Monochrome Single-Scan Mode                                    |         |    |

|   |     |          | 7.5.1.1     | Signals                                                        |         |    |

|   |     |          | 7.5.1.1     | Schematics/Block Diagram                                       |         |    |

|   |     |          | 7.5.1.3     | Layout Notes                                                   |         |    |

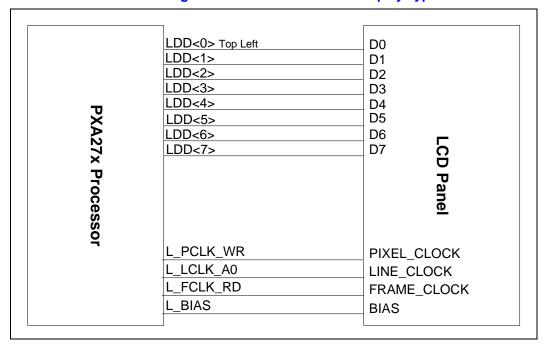

|   |     | 7.5.2    |             | Monochrome Single-Scan Double-Pixel Mode                       |         |    |

|   |     |          |             | 9                                                              |         | _  |

|   |        |           | 7.5.2.1            | Signals                                                   |    |              |          |

|---|--------|-----------|--------------------|-----------------------------------------------------------|----|--------------|----------|

|   |        |           | 7.5.2.2            | Schematics / Block Diagram                                |    |              |          |

|   |        |           | 7.5.2.3            | Layout Notes                                              |    | II: <i>1</i> | -9       |

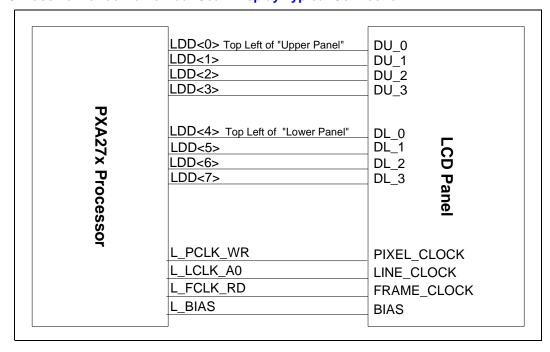

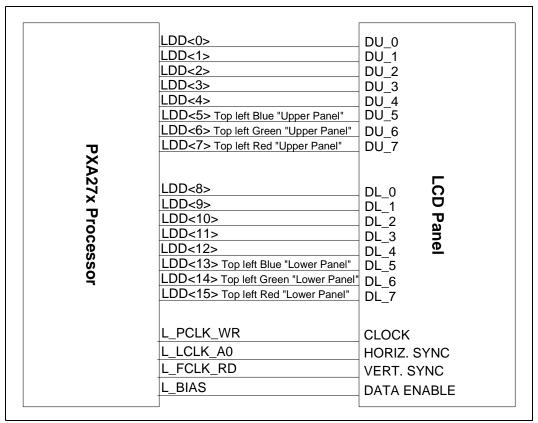

|   |        | 7.5.3     |                    | Monochrome Dual-Scan Mode                                 |    |              |          |

|   |        |           | 7.5.3.1            | Signals                                                   |    | II: 7<br>_   | -9       |

|   |        |           | 7.5.3.2            | Schematics / Block Diagram                                | ll | : 7-         | 10       |

|   |        |           | 7.5.3.3            | Layout Notes                                              |    |              |          |

|   |        | 7.5.4     |                    | Color Single-Scan Mode                                    |    |              |          |

|   |        |           | 7.5.4.1            | Signals                                                   |    |              |          |

|   |        |           | 7.5.4.2            | Schematics/Block Diagram                                  |    |              |          |

|   |        |           | 7.5.4.3            | Layout Notes                                              |    |              |          |

|   |        | 7.5.5     |                    | Color Dual-Scan Mode                                      |    |              |          |

|   |        |           | 7.5.5.1            | Signals                                                   |    |              |          |

|   |        |           | 7.5.5.2            | Schematics / Block Diagram                                |    |              |          |

|   |        | 7.5.0     | 7.5.5.3            | Layout Notes                                              |    |              |          |

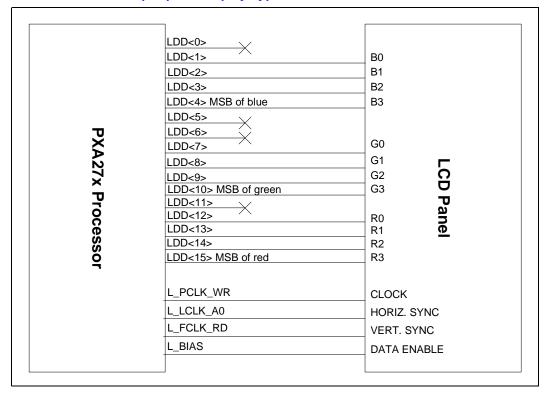

|   |        | 7.5.6     |                    | olor 12-bit per pixel Mode                                |    |              |          |

|   |        |           | 7.5.6.1            | Signals                                                   |    |              |          |

|   |        |           | 7.5.6.2            | Schematics / Block Diagram                                |    |              |          |

|   |        |           | 7.5.6.3            | Layout Notes                                              |    |              |          |

|   |        | 7.5.7     |                    | color, 16-bit per pixel Mode                              |    |              |          |

|   |        |           | 7.5.7.1            | Signals                                                   |    |              |          |

|   |        |           | 7.5.7.2            | Schematics / Block Diagram                                | II | : /-ˈ        | 17       |

|   |        | 7.5.0     | 7.5.7.3            | Layout Notes                                              |    |              |          |

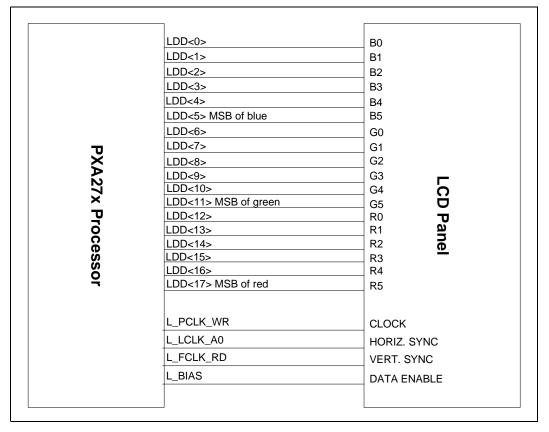

|   |        | 7.5.8     |                    | color, 18-bit per pixel Mode                              |    |              |          |

|   |        |           | 7.5.8.1            | Signals                                                   |    |              |          |

|   |        |           | 7.5.8.2            | Schematics / Block Diagram                                |    |              |          |

|   |        | 7.5.0     | 7.5.8.3            | Layout Notes                                              |    |              |          |

|   |        | 7.5.9     |                    | anel                                                      |    |              |          |

|   |        |           | 7.5.9.1            | Signals                                                   | II | : /-/        | 21<br>24 |

|   |        |           | 7.5.9.2<br>7.5.9.3 | Schematics / Block Diagram                                |    |              |          |

|   |        |           | 7.5.9.5            | Layout Notes                                              |    | . /-/        |          |

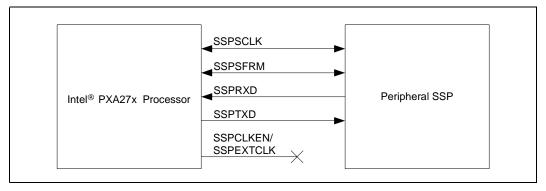

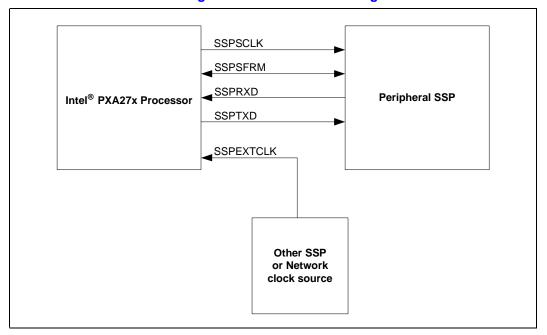

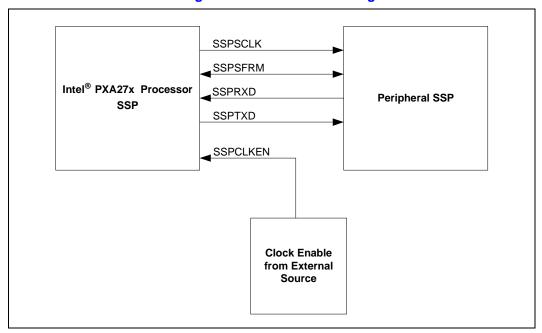

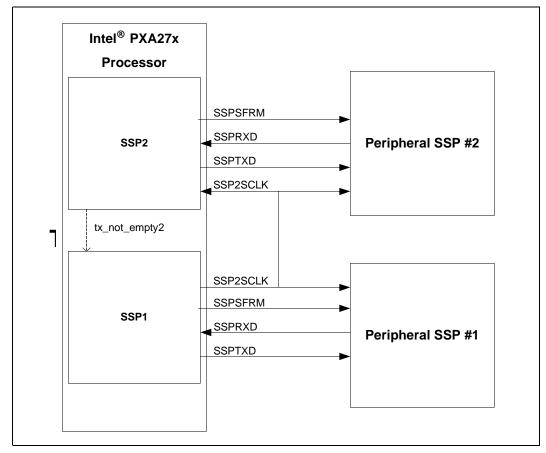

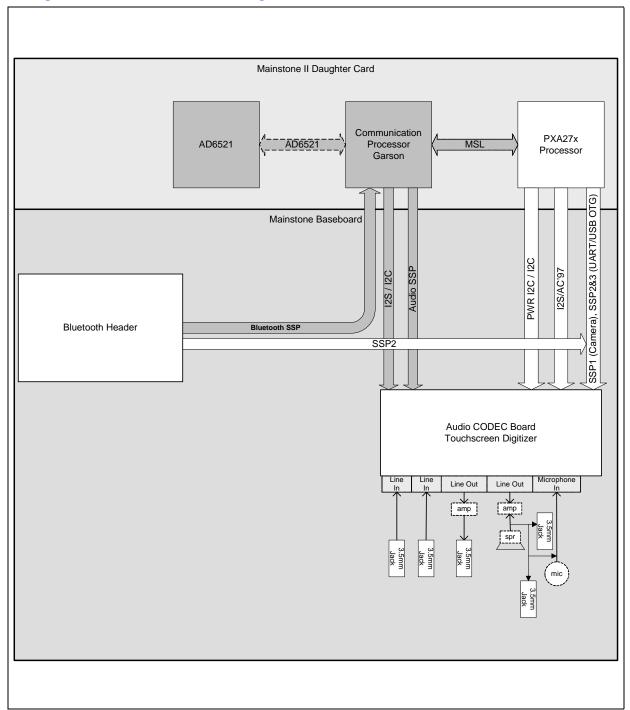

| 8 | SSP    | Port Inte | erface             |                                                           |    | II: 8        | -1       |

|   | 8.1    | Overvie   | 2///               |                                                           | 1  | اا و         | 1        |

|   | 8.2    |           |                    |                                                           |    |              |          |

|   | 8.3    |           |                    |                                                           |    |              |          |

|   | 0.3    | 8.3.1     |                    | d SSP Configuration Scheme                                |    |              |          |

|   |        | 8.3.2     |                    | Clock Source Configuration Scheme                         |    |              |          |

|   |        |           |                    |                                                           |    |              |          |

|   |        | 8.3.3     | External           | Clock Enable Configuration Scheme                         |    | II. 8        | ,-o      |

|   | 0.4    | 8.3.4     |                    | (to PXA27x Processor) Clock Enable Configuration Design . |    |              |          |

|   | 8.4    | Layout    | notes              |                                                           |    | II: 8        | -b       |

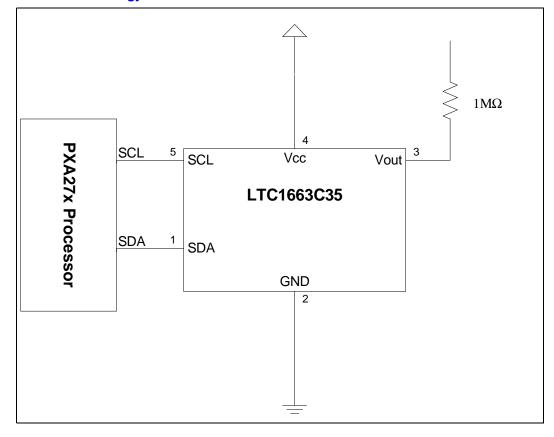

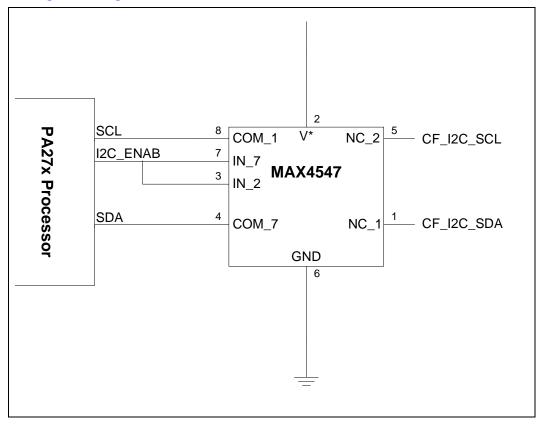

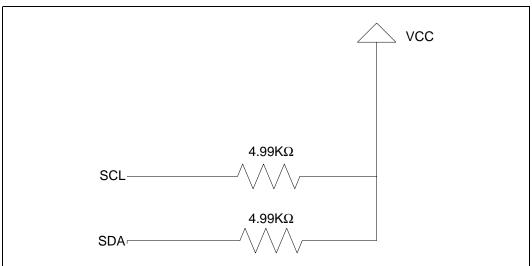

| 9 | Inter- | Integrat  | ed Circui          | it (I2C)                                                  |    | II: 9        | )-1      |

|   | 9.1    | _         |                    | ` '                                                       |    |              |          |

|   | 9.1    |           |                    |                                                           |    |              |          |

|   |        |           |                    | / Diagram                                                 |    |              |          |

|   | 9.3    |           |                    | C Diagram                                                 |    |              |          |

|   |        | 9.3.1     |                    | o-Analog Converter (DAC)                                  |    |              |          |

|   |        | 9.3.2     |                    | ses of I2C                                                |    |              |          |

|   | 0.4    | 9.3.3     |                    | and Pull-Downs                                            |    |              |          |

|   | 9.4    | Layout    | Notes              |                                                           |    | II: 9        | -4       |

| 10.1   Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 | UART   | 「Interfa | ces                                             | II: 10-1              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|----------|-------------------------------------------------|-----------------------|

| 10.2 Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 10.1   | Overvie  | ew                                              | II: 10-1              |

| 10.3 Types of UARTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 10.2   |          |                                                 |                       |

| 10.3.1 Full Function UART   II: 10-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 10.3   |          |                                                 |                       |

| 10.3.1.1 Full Function UART Signals.   II: 10.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |        |          |                                                 |                       |

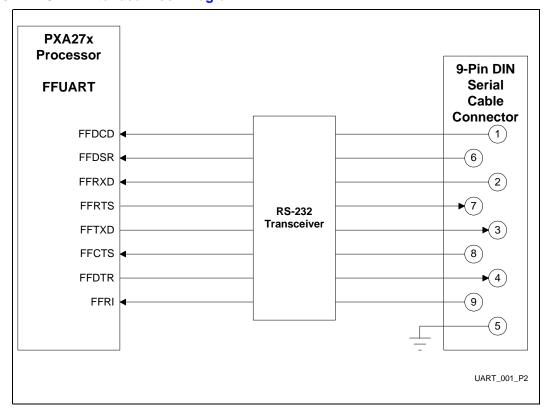

| 10.3.1.2 FFUART Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |        |          |                                                 |                       |

| 10.3.1.3 FFUART Layout Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |        |          | 10.3.1.2 FFUART Block Diagram                   | II: 10-4              |

| 10.3.2.1 Bluetooth UART Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |        |          |                                                 |                       |

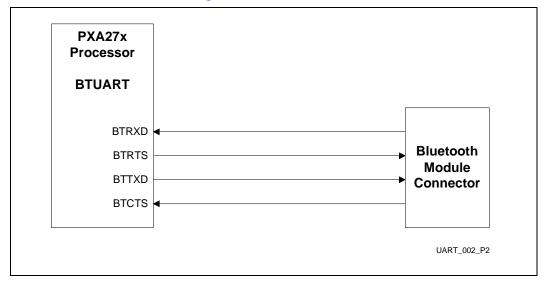

| 10.3.2.1 Bluetooth UART Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |        | 10.3.2   | Bluetooth UART                                  | II: 10-5              |

| 10.3.3   Standard UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |        |          |                                                 |                       |

| 10.3.3.1 Standard UART Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |        |          | 10.3.2.2 Bluetooth UART Block Diagram           | II: 10-5              |

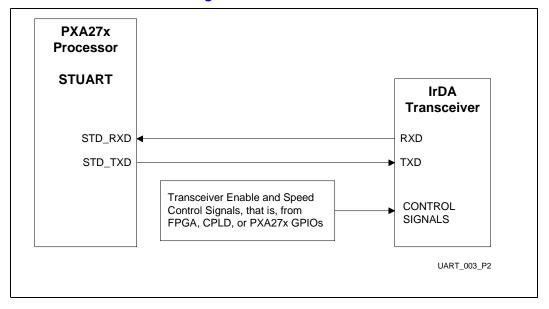

| 10.3.3.2 Standard UART Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |        | 10.3.3   | Standard UART                                   | II: 10-6              |

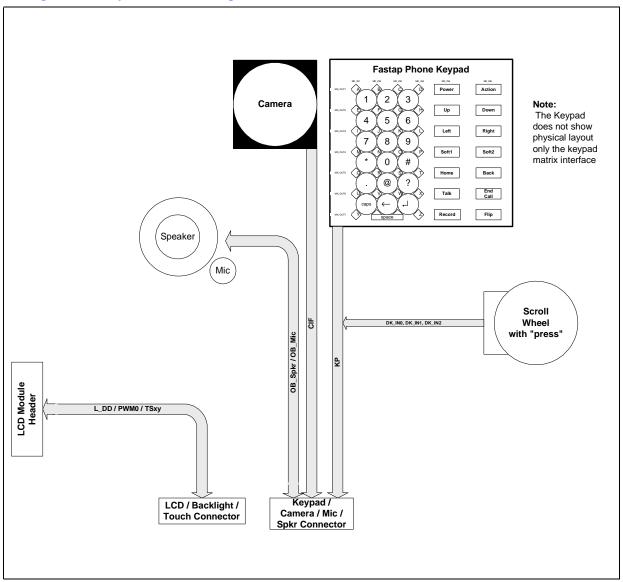

| 11   Fast Infrared Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |        |          | 10.3.3.1 Standard UART Signals                  | II: 10-6              |

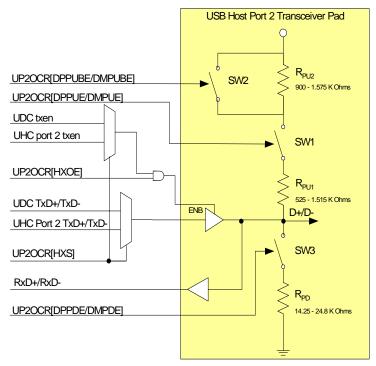

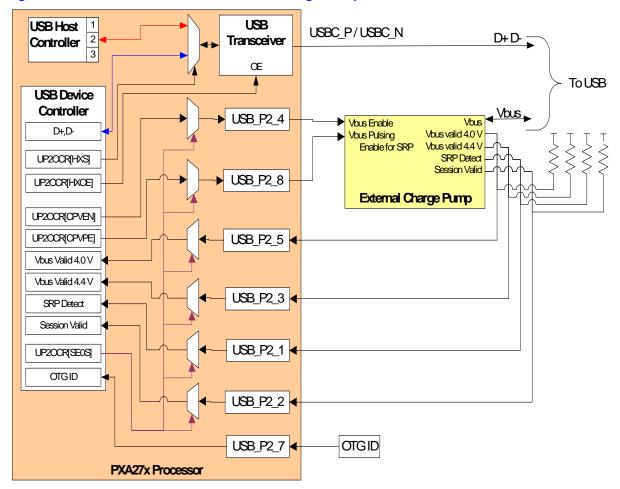

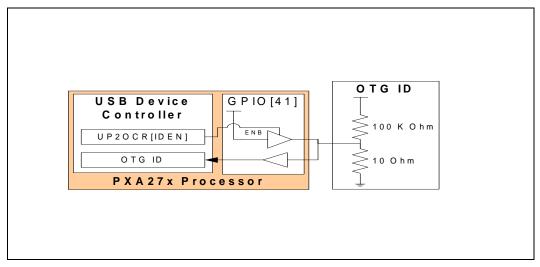

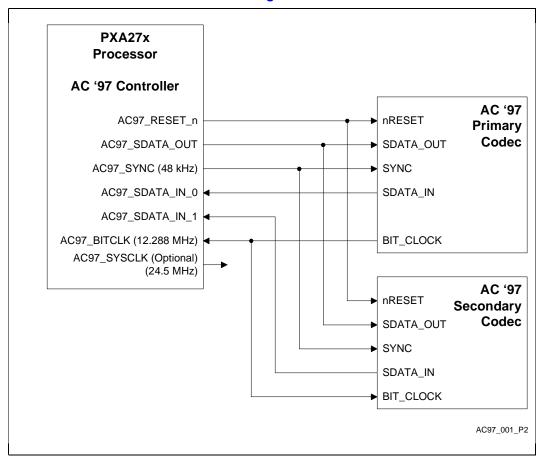

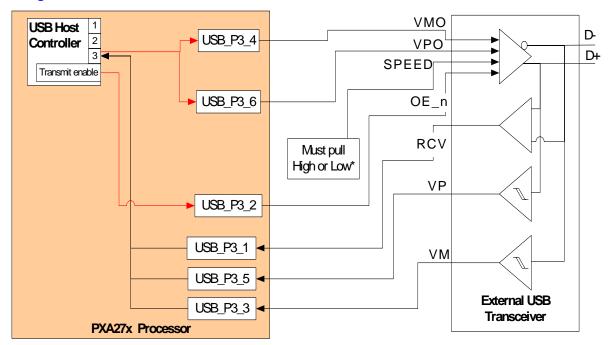

| 11.1 Overview       II: 11-1         11.2 Signals       II: 11-1         11.3 Block Diagram       II: 11-2         12 'USB Client Controller       II: 12-1         12.1 Overview       II: 12-1         12.2 Signals       II: 12-1         12.3 Block Diagram       II: 12-2         12.4 Layout Notes       II: 12-2         12.4.1 Self-Powered Devices       II: 12-2         12.4.1.1 Operation if GPIOn and GPIOx are Different Pins       II: 12-3         12.4.2 Bus-Powered Device       II: 12-6         12.4.3 USB On-The-GO Transceiver Usage       II: 12-6         12.4.4 Interface to External Transceiver (OTG)       II: 12-8         12.4.5 Interface to External Charge Pump Device (OTG)       II: 12-9         12.4.6 OTG ID       II: 12-11         12.4.7 Interface to External USB Transceiver (non-OTG)       II: 12-12         13 AC '97       II: 13-1         13.1 Overview       II: 13-1         13.2 Signals       II: 13-1         13.3 Block Diagram       II: 13-1         14.4 Layout Notes       II: 13-3         14.5 Modes of Operation Overview       II: 14-4         14.5 Modes of Operation Overview       II: 14-4         14.5.1.1 Signals       II: 14-4         14.5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |        |          |                                                 |                       |

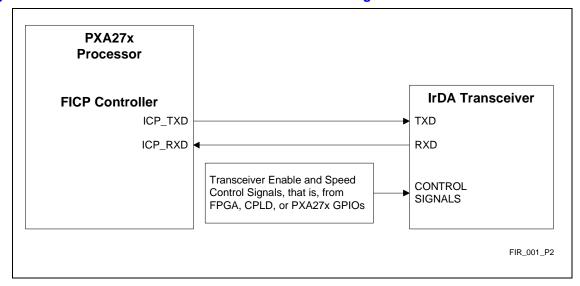

| 11.1 Overview       II: 11-1         11.2 Signals       II: 11-1         11.3 Block Diagram       II: 11-2         12 'USB Client Controller       II: 12-1         12.1 Overview       II: 12-1         12.2 Signals       II: 12-1         12.3 Block Diagram       II: 12-2         12.4 Layout Notes       II: 12-2         12.4.1 Self-Powered Devices       II: 12-2         12.4.1.1 Operation if GPIOn and GPIOx are Different Pins       II: 12-3         12.4.2 Bus-Powered Device       II: 12-6         12.4.3 USB On-The-GO Transceiver Usage       II: 12-6         12.4.4 Interface to External Transceiver (OTG)       II: 12-8         12.4.5 Interface to External Charge Pump Device (OTG)       II: 12-9         12.4.6 OTG ID       II: 12-11         12.4.7 Interface to External USB Transceiver (non-OTG)       II: 12-12         13 AC '97       II: 13-1         13.1 Overview       II: 13-1         13.2 Signals       II: 13-1         13.3 Block Diagram       II: 13-1         14.4 Layout Notes       II: 13-3         14.5 Modes of Operation Overview       II: 14-4         14.5 Modes of Operation Overview       II: 14-4         14.5.1.1 Signals       II: 14-4         14.5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 | East I | nfrarad  | Interface                                       | II. 11 1              |

| 11.2   Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 |        |          |                                                 |                       |

| 11.3 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 11.1   |          |                                                 |                       |

| 12 'USB Client Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 11.2   |          |                                                 |                       |

| 12.1   Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 11.3   | Block D  | Diagram                                         | II: 11-2              |

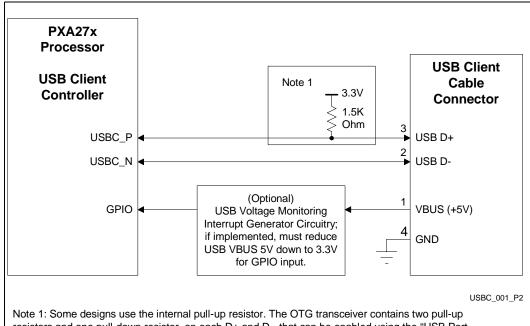

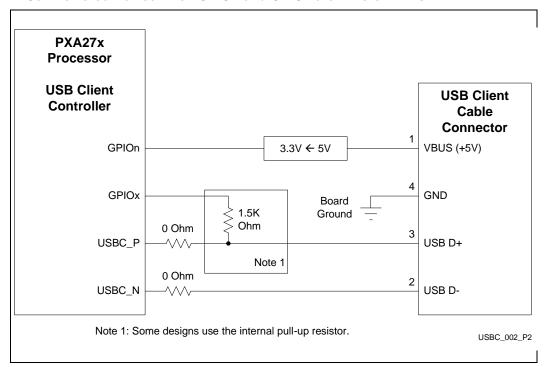

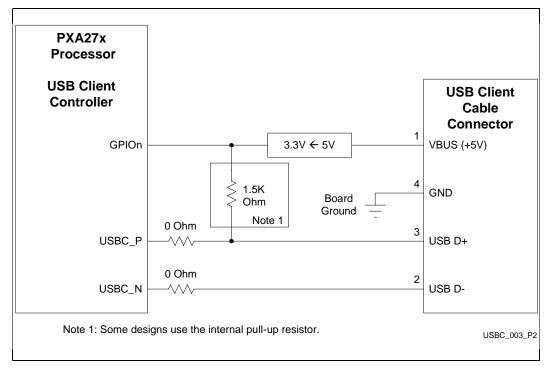

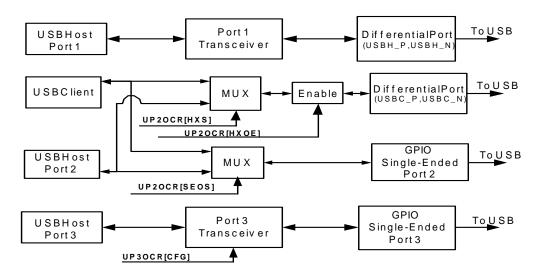

| 12.1   Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12 | HICR   | Cliont C | Controller                                      | II: 12 <sub>-</sub> 1 |

| 12.2   Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 |        |          |                                                 |                       |